# Caller Line ID on the CMX860, CMX867 and CMX868

Caller Line ID (CLI) was originally developed for the US market but has become commonplace throughout the World because of its multitudinous applications.

There are a number of CLI protocols to which telephone equipment manufacturers must comply. This document gives an overview of two types; BELL GR-30-CORE/SR-TSV-002476 (or ETSI 300 659-1 section 6.1.1) used in the USA and most of the world and Caller Line Identification Presentation (CLIP) BT SIN 227 (or ETSI ETS 300 659-1 section 6.1.2c) used in the UK.

CLI operates in two distinctly different modes, on-hook and off-hook, which are often referred to as type 1 and type 2 respectively. The on-hook mode is the most widely used because the CLI is delivered before the call is accepted. Here the calling parties identity may be used within the system in a decision making process. For example, a simple call filter that rejects calls from callers who withhold their own number. Off-hook systems find more limited use because the target function is to let the called party know that they have missed a call. This document covers only on-Hook or type 1 CLI although the principles may be extended for some type 2 services. Whilst the core function of CMX868 and CMX867 are specifically targeted at modem applications CLI can be a necessary feature of the overall design. For example, CLI can assist in fraud prevention by stopping an unauthorised caller from blocking a POS terminals modem making credit check calls. CLI may even be provided as a 'value added' feature. The CMX860 is targeted at applications such as least cost routing. Here CLI can be a useful security feature in Least Cost Routers permitting only the authorised caller to provide call table updates using remote access.

The CMX868, CMX867 and CMX860 include a Ring Detector, 1200bps FSK Demodulator and a Programmable Tone Pair Detector that can be used to detect and extract the CLI message string. This text describes the Bell and BT systems and concludes with three algorithms that can form the basis of user code.

- · Bellcore On-Hook CLI.

- BT On-Hook CLI

- Retrieving the CLI data

For applications where both Bellcore and BT compatibility is required it is possible to combine both algorithms to make one common solution.

**Consumer Microcircuits Limited**

Oval Park, Langford, Maldon, Essex, CM8 6WG, England

tel: +44 (0)1621 875500 Fax: +44 (0)1621875600 e-mail: support@cmlmicro.co.uk - www.cmlmicro.co.uk

# 2.0 Bellcore and BT CLI formats

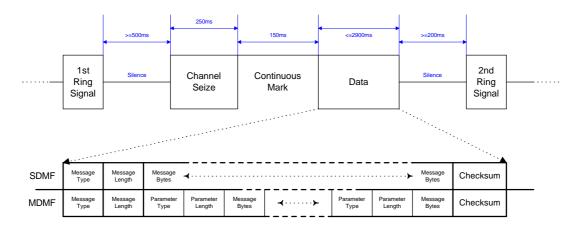

2.1 Figures 1 and 2 illustrate the line signalling and data format for both Bellcore and BT systems. The data checksum can only be used to validate the data; no additional error correction is added. If an error occurs the Central Office or exchange cannot retransmit this information.

SDMF = Single Data Message Format MDMF = Multiple Data Message Format

Fig.1 Bellcore On-hook System Signals and Data Format

Fig.2 BT On-hook System Signals and Data Format

2.2 In the Bellcore scheme the start of CLI is signalled with a ringing signal that is likely to exceed 40V. The BT scheme signals by a line reversal where the potential between the two wires will be greater than 15V. The CMX868, CMX867 and CMX860 Data Sheets give information on a Ring Detect scheme. If required a suitably adjusted Ring Detect circuit, where voltage limiting of the ringing signal is provided, can be used to measure the ringing cadence.

- 2.3 If no CLI is present on a Bellcore system then the silence period between rings may extend for 4 seconds (nominal)

- 2.4 For some applications the Channel Seizure on BT systems may be delayed by up to 5 seconds. Either or both silent periods may be extended in this case.

- 3.0 General Notes.

- 3.1 Interface details, line level specifications etc are not specified because these are dependent on the application and the intended country of operation. For this information please contact your local PTT or refer to the relevant specifications.

- 3.2 The following syntax is used to describe the CMX868, CMX867 and CMX860 C-Bus registers.

- 1. *General Control* (\$E0) The register name is given italics followed by the hexadecimal address of the register in brackets.

- 2. b2 = 1 The register bit, bit 2 is set to a 1.

- 3. b5..b2 = 1001 The register bits, bit 5 through bit 2 are set to 1001 respectively.

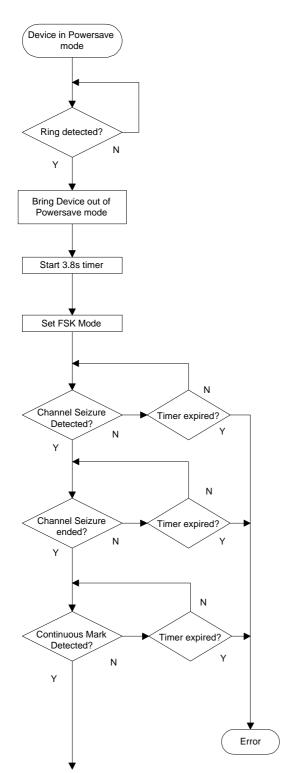

- 3.3 Figures 3 & 4 both assume that the CMX868, CMX867 and CMX860 are powered up and a General Reset Command C-BUS address \$01 (no data) has been issued (alternatively set RESETN pin low then high for the CMX860) then:

Write to the General Control (\$E0) register

b7 = 1 (reset internal circuitry)

b8 = 1 (select normal operating mode)

Wait 20ms

2

Write to the *General Control* (\$E0) register

b8 = 0 (powersave mode selected)

b6 = 1 (enable IRQN output)

b5 = 1 (unmask Ring Detect IRO)

The CMX868, CMX867 and CMX860 will be in powersave mode but programmed to interrupt the controlling microcontroller when ringing is detected.

- 3.4 The Status Register IRQ bit, b15, should always be used to qualify IRQs.

- 3.5 The Status Register Energy Detect bit, b10, should be used to qualify all pattern detects and demodulated data when Rx Modem Modes are selected.

- 3.6 The Default coefficients for the Programmable Tone Pair Detector are suitable for detecting the CAS tone on BT CLIP.

- 3.7 Additional timers and error handling may be required. For example consider if a TE Loop State condition was applied during a CLI transaction then the processor must detect this and force the CLI software routine to terminate.

# **Ring Detected?**

Status (\$E6)

b14 = 1 (Ring Detect bit set)

# **Bring Device out of Powersave mode**

General Control (\$E0)

b5 = 0 (Mask Ring Detect IRQ)

b8 = 1 (Powerup enabled) b7 = 1 (Device Internal Circuits Reset)

wait 20ms

b7 = 0 (Normal Mode selected)

# Start 3.8 second timer

# **Set FSK Mode**

Receive Mode (\$E2)b

b15..12 = 0011 (Bell 202 1200bps FSK mode) b11..9 = User defined (Rx Level) b5..3 = 0xx (USART disabled)

# **Detect Channel Seizure**

Use 1010 Pattern Detect and FSK Energy Detect to indicate the presence of a channel siezure. General Control (\$E0)

b1 = 1 (Unmask 1010 Pattern Detect IRQ)

On interrupt monitor Status Register (\$E6) b10 = 1 and b9 = 1 (valid 1010 pattern detected).

# **Channel Seizure ended**

The presence of the channel siezure should be tested periodically to confirm that is still being received.

Poll Status Register (\$E6) b10 = 1 (in-band energy detected)

b9 = 1 if a valid channel siezure is being detected

b9 = 0 when the channel siezure ends.

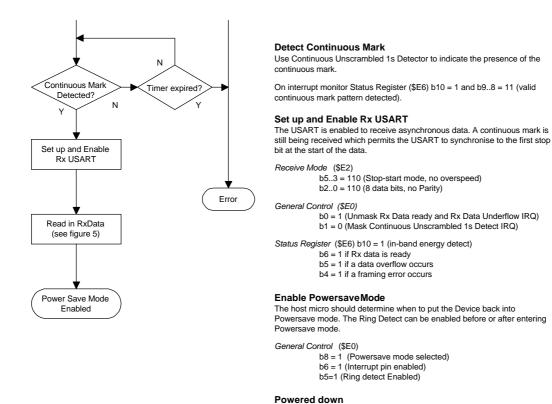

# **Detect Continuous Mark**

Use Continuous Unscrambled 1s Detector to indicate the presence of the continuous mark.

On interrupt monitor Status Register (\$E6) b10 = 1 and b8..7 = 01 (valid continuous unscrambled mark pattern detected).

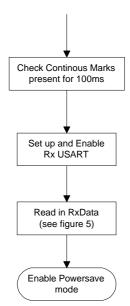

Fig.3 Bell on-hook CLI algorithm

# Check Continuous Marks present for 100ms

The presence of the continuous marks should be tested periodically to confirm that is still being received.

Poll Status Register (\$E6) b10 = 1 and b8..7 = 01 if a valid channel siezure is being detected

# Set up and Enable Rx USART

The USART is enabled to receive asynchronous data. A continuous mark is still being received which permits the USART to synchronise to the first stop bit at the start of the data.

Receive Mode (\$E2)

b5..3 = 110 (Stop-start mode, no overspeed) b2..0 = 110 (8 data bits, no Parity)

General Control (\$E0)

b0 = 1 (Unmask Rx Data ready and Rx Data Underflow IRQ)

b1 = 0 (Mask Continuous Unscrambled 1s

Detect IRQ)

Status Register (\$E6) b10 = 1 (in-band energy detect)

b6 = 1 if Rx data is ready b5 = 1 if a data overflow occurs b4 = 1 if a framing error occurs

# **Enable Powersave Mode**

The host micro should determine when to put the Device back into Powersave mode. The Ring Detect can be enabled before or after entering Powersave mode.

General Control (\$E0)

b8 = 1 (Powersave mode selected) b6 = 1 (Interrupt pin enabled)

b5=1 (Ring detect Enabled)

Fig.3 Bell on-hook CLI algorithm (Continued)

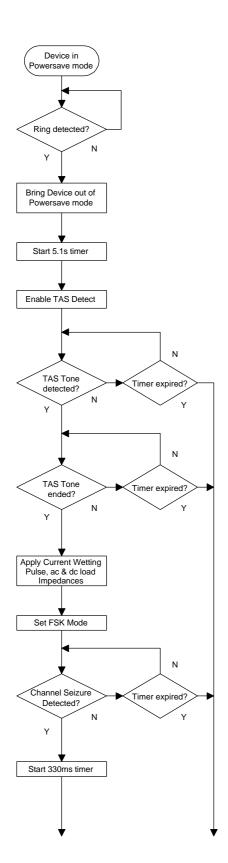

# Ring detected

Line reversal or ringing Status (\$E0)

b14 = 1 (Ring Detect bit set)

# **Bring Device out of Powersave mode**

General Control (\$E0)

b5 = 0 (Mask Ring Detect IRQ)

b8 = 1 (Powerup enabled)

b7 = 1 (Device Internal Circuits Reset)

wait 20ms

b7 = 0 (Normal Mode selected)

# Start 5.1s timer

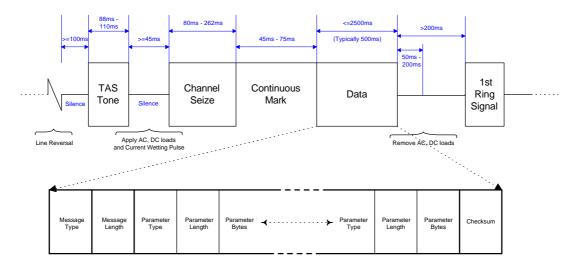

#### **Detect TAS tone**

Both Programmable Tone Detectors are used to detect the Idle State Tone Alert Signal (TAS)

General Control (\$E0)

b2 = 1 (Unmask Both Programmable Tones Detected IRQ)

Receive Mode (\$E2)

b15..b12 = 0001 (Tone Detect mode)

b11..9 = user defined (Rx level adjust) b2..0 = 100 (select Programmable Tone Pair Detector)

On interrupt Status (\$E6)

b10 = 1 (TAS tone present)

### TAS Tone ended

Monitor Status (\$E6) until b10 = 0 (TAS tone dissapeared)

# Apply Current Wetting Pulse, ac & dc load Impedances

The TE should respond to the Idle State Tone Alert Signal by drawing a dc Wetting pulse and applying a dc load and an ac load. The dc Wetting Pulse is applied during the silent period following the end of the TAS. The ac Load is applied at the same time as the wetting pulse and is removed at end of the V.23 signals. The dc Load is applied and removed at the same time as the ac load.

# Set FSK Mode

Receive Mode (\$E2)

b15..12 = 0101 (V.23 1200bps FSK Mode)

b11..9 = user defined (Rx Level adjust) b5..3 = 0xx (USART Disabled)

# **Detect Channel Seizure**

Use 1010 Pattern Detect and FSK Energy Detect to indicate the presence of a channel siezure.

General Control (\$E0)

b1 = 1 (Unmask 1010 Pattern Detect IRQ)

On interrupt monitor Status Register (\$E6) b10 = 1 and b9 = 1 (valid 1010 pattern detected) for approximately 40ms.

# Start 330ms timer

Cancel 5.1s timer and start a 330ms timer

Fig.4 BT on-hook CLI algorithm (Continued)

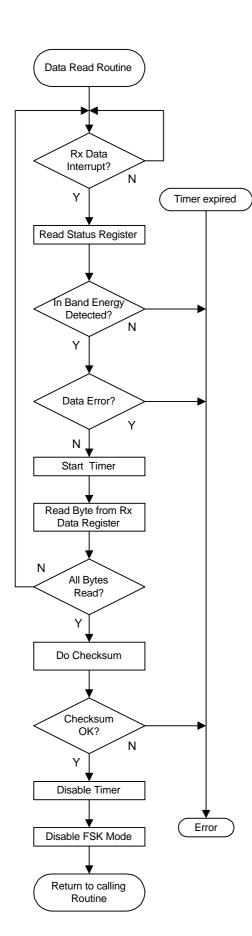

General Control (\$E0)

b5=1

b8..6=001 (Power down & Interrupt pin enabled) (Ring detect enabled)

# **Read Status Register**

Status (\$E6)

b10 = 1 (in-band energy detect) b6 = 1 (Rd Data Ready)

b5 = 1 if a data overflow occurs

b4 = 1 if a framing error occurs

# **Start Timer**

If this is the first byte of the message then start a timer.

BT start a 2.6 second timer.

Bell start 2.9 second timer.

If this timer expires before the CLIP has been completely received then an error has occured.

# Read Byte from Rx Data Register

The first Data Byte is the message type

BT 0x80 for CLIP.

Bell 0x40 for SDMF and 0x80 for MDMF

The second Data Byte is the remainder of the message length in bytes but does not include the final two checksum bytes.

# Do Checksum

The last two bytes read are the checksum. Do a modulo-2 addition of all of the received bytes including the two checksum bytes but ignore any carries. The result should be zero or an error has occured.

Fig. 5 Retrieving the CLI data

# 5.0 Glossary of terms

Channel Seizure A "10101..." bit pattern.

CIDCW Calling Identity Delivery on Call Waiting – While a telephone

conversation between two individuals is taking place it is possible to let a

third party's identification reach the off-hook answering modem.

DTAS/CAS Dual-tone Alerting Signal/Caller Alert Signal – This dual tone is typically

2130Hz + 2750Hz.

Mark A "11111..." bit pattern.

SDT Stuttered Dial Tone – When there is a message waiting in a customer's

voice-mail box, the telephone company's Central Office switch may apply a cadenced dial tone to the customers line when it is taken off-hook,

indicating that a message has been left.

VMWI Visual Message Waiting Indicator – This is an indicator for a group of

services that is offered by telephone companies to their customers. For example, it allows voice messages to be stored for later retrieval by the

subscribing customer (Voice mail notification).

# Caller Line ID on the CMX860, CMX867 and CMX868

# **Amendment Record**

| AN/Telecom/CLI/2 June 2001  | Original       |

|-----------------------------|----------------|

| AN/Telecom/CLI/3 March 2004 | Fig 3 Modified |

|                             |                |

|                             |                |

|                             |                |